NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (NAAC Accredited) (Approved by AICTE, Affiliated to APJ Abdul Kalam Technological University, Kerala)

### DEPARTMENT OF MECHATRONICS ENGINEERING

# **COURSE MATERIALS**

# **MR 405 EMBEDDED SYSTEMS**

# VISION OF THE INSTITUTION

To mould true citizens who are millennium leaders and catalysts of change through excellence in education.

### MISSION OF THE INSTITUTION

**NCERC** is committed to transform itself into a center of excellence in Learning and Research in Engineering and Frontier Technology and to impart quality education to mould technically competent citizens with moral integrity, social commitment and ethical values.

We intend to facilitate our students to assimilate the latest technological know-how and to imbibe discipline, culture and spiritually, and to mould them in to technological giants, dedicated research scientists and intellectual leaders of the country who can spread the beams of light and happiness among the poor and the underprivileged.

### **ABOUT DEPARTMENT**

- Established in: 2013

- Course offered: B.Tech Mechatronics Engineering

- Approved by AICTE New Delhi and Accredited by NAAC

- Affiliated to the University of Dr. A P J Abdul Kalam Technological University.

### **DEPARTMENT VISION**

To develop professionally ethical and socially responsible Mechatronics engineers to serve the humanity through quality professional education.

### **DEPARTMENT MISSION**

1) The department is committed to impart the right blend of knowledge and quality education to create professionally ethical and socially responsible graduates.

2) The department is committed to impart the awareness to meet the current challenges in technology.

3) Establish state-of-the-art laboratories to promote practical knowledge of mechatronics to meet the needs of the society

### **PROGRAMME EDUCATIONAL OBJECTIVES**

I. Graduates shall have the ability to work in multidisciplinary environment with good professional and commitment.

II. Graduates shall have the ability to solve the complex engineering problems by applying electrical, mechanical, electronics and computer knowledge and engage in lifelong learning in their profession.

III. Graduates shall have the ability to lead and contribute in a team with entrepreneur skills, professional, social and ethical responsibilities.

IV. Graduates shall have ability to acquire scientific and engineering fundamentals necessary for higher studies and research.

### **PROGRAM OUTCOME (PO'S)**

### **Engineering Graduates will be able to:**

**PO 1. Engineering knowledge:** Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

**PO 2. Problem analysis:** Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

**PO 3. Design/development of solutions:** Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

**PO 4. Conduct investigations of complex problems:** Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

**PO 5. Modern tool usage:** Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

**PO 6. The engineer and society:** Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

**PO 7. Environment and sustainability:** Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

**PO 8. Ethics:** Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

**PO 9. Individual and team work:** Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

**PO 10. Communication:** Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

**PO 11. Project management and finance:** Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

PO 12. Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

### **PROGRAM SPECIFIC OUTCOME (PSO'S)**

**PSO 1:** Design and develop Mechatronics systems to solve the complex engineering problem by integrating electronics, mechanical and control systems.

**PSO 2:** Apply the engineering knowledge to conduct investigations of complex engineering problem related to instrumentation, control, automation, robotics and provide solutions.

### **COURSE OUTCOME**

### After the completion of the course the student will be able to

| CO 1 | Acquire knowledge to design a embedded system                                |

|------|------------------------------------------------------------------------------|

| CO 2 | Describe about the hardware and software components of embedded system       |

| CO 3 | Acquire knowledge on custom single purpose processor design and optimization |

| CO 4 | Interpret about the general purpose processors                               |

| CO 5 | Understand the concepts of common memory devices.                            |

| CO 6 | Explain about various software development tools and RTOS                    |

### CO VS PO'S AND PSO'S MAPPING

| CO          | <b>PO1</b> | PO | PO3 | PO | PO5 | <b>PO6</b> | <b>PO7</b> | <b>PO8</b> | <b>PO9</b> | <b>PO10</b> | PO11 | <b>PO12</b> | PS0 | PSO |

|-------------|------------|----|-----|----|-----|------------|------------|------------|------------|-------------|------|-------------|-----|-----|

|             |            | 2  |     | 4  |     |            |            |            |            |             |      |             | 1   | 2   |

| <b>CO 1</b> | 3          | 1  | 2   | 2  |     | -          | -          | -          | -          | -           | -    | 3           | 3   | 2   |

| CO 2        | 3          | -  | 2   | 2  | -   | •          | -          | -          | -          | -           | -    | 3           | 3   | 2   |

| CO 3        | 3          | -  | 2   | 2  | -   | -          | -          | -          | -          | -           | -    | 3           | 3   | 2   |

| <b>CO 4</b> | 3          | -  | 2   | 2  |     | -          | -          | -          | -          | -           | -    | 3           | 3   | 2   |

| CO 5        | 3          | -  | 2   | 2  | -   | -          | -          | -          | -          | -           | -    | 3           | 3   | 2   |

| <b>CO 6</b> | 3          | -  | 2   | 2  | -   | -          | -          | -          | -          | -           | -    | 3           | 3   | 2   |

Note: H-Highly correlated=3, M-Medium correlated=2, L-Less correlated=1

### **SYLLABUS**

| Course code                                                | Course Name                                                                                                                                                     | L-T-P - Credits                                                                      | Year of<br>Introduction                  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------|

| MR405                                                      | Embedded Systems                                                                                                                                                | 3-0-0-3                                                                              | 2016                                     |

| Prerequisite : NII                                         | M                                                                                                                                                               |                                                                                      | an a |

| programmi<br>system.<br>• To give stu<br>embedded s        | students familiar with the arching models, tools for embedded syst<br>adents knowledge on the hardware<br>systems design.<br>students to the concepts of embedd | tem design and implement:<br>and real time operating sy                              | ation of embedded                        |

| embedded system<br>specific instructio<br>processors-Commo |                                                                                                                                                                 | om Single-purpose proces<br>pose processors- Standar<br>evices - Serial devices - Pa | ssors- Application<br>d single-purpose   |

| <ul> <li>the basic co</li> <li>the design t</li> </ul>     | s of embedded systems<br>incepts of real time Operating syste<br>echniques to develop software for a<br>purpose operating systems and the                       | embedded systems                                                                     |                                          |

| -                                                          | r-r                                                                                                                                                             | the state of the state of the state                                                  |                                          |

| McGraw-H                                                   | l, "Embedded Systems – Architectu<br>ill Publishing Company Ltd., New<br>Vahid and Tony Givargis,                                                               | Delhi, 2010.<br>Embedded System Des                                                  |                                          |

| Hardware/                                                  | Software Introduction, Wiley, 2002.<br>Simon, "An embedded software pri                                                                                         |                                                                                      | Asia 2001.                               |

| Course Plan |                                                                                                                                                                                              |       |                    |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|--|--|

| Module      | Contents                                                                                                                                                                                     | Hours | Sem. Exam<br>Marks |  |  |

| I           | Embedded system- Functional building block of embedded system-<br>Characteristics of embedded system applications- Challenges in<br>embedded system design- Embedded system design processes | 7     | 15%                |  |  |

| п           | Classification - Processors in the system - Other h/w units. Software<br>components - Typical applications - Embedded systems on a chip<br>(SoC) and use of VLSI circuits.                   | 7     | 15%                |  |  |

|             | FIRST INTERNAL EXAMINATION                                                                                                                                                                   |       |                    |  |  |

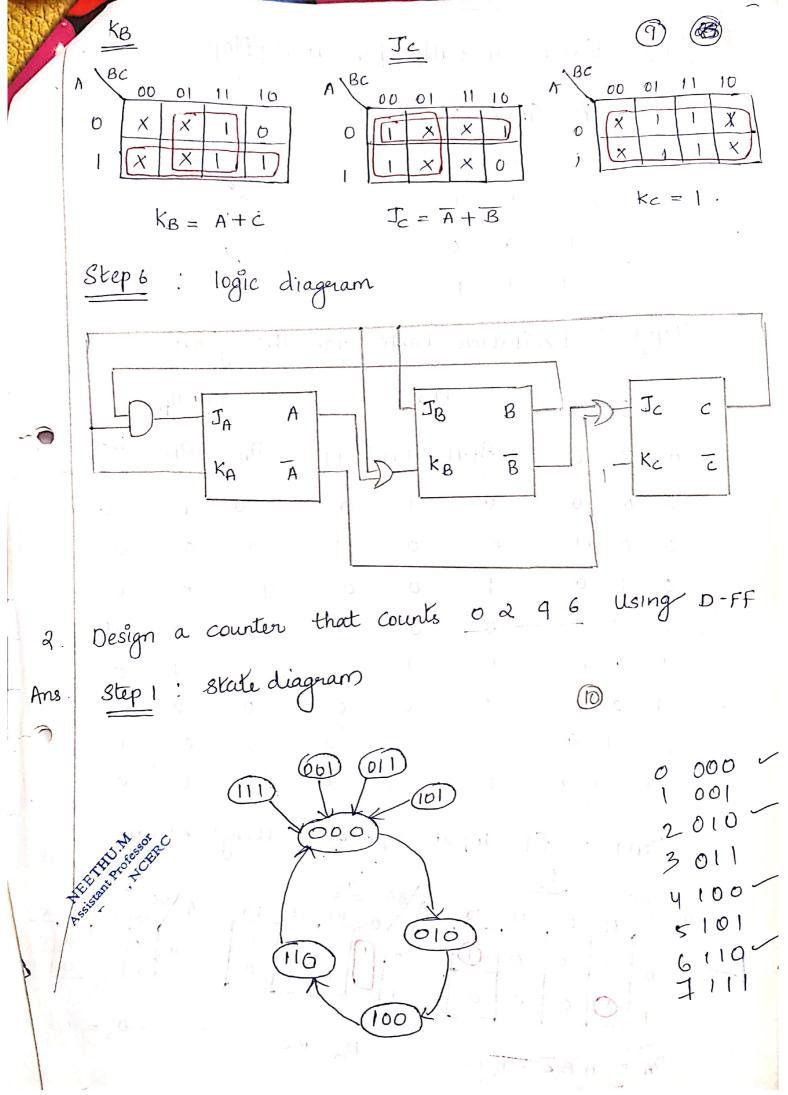

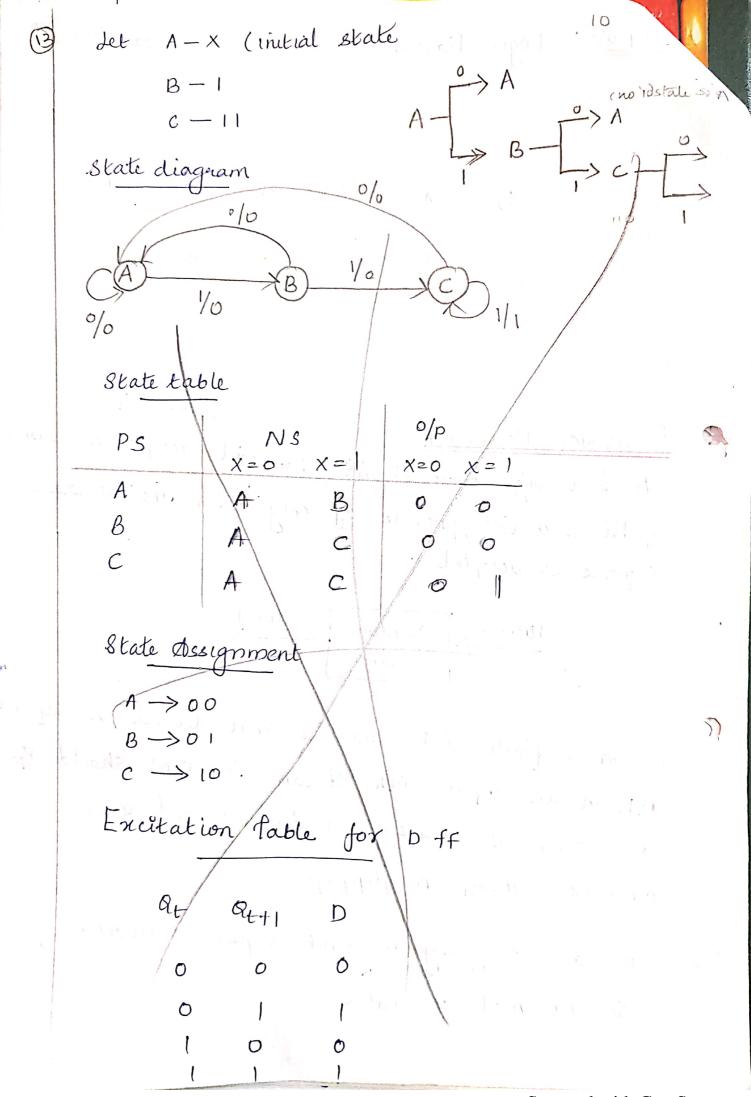

| ш  | Custom Single-purpose processors : Hardware-Combinational<br>Logic- Transistors and logic gates- Basic combinational and<br>Sequential logic design- Custom single purpose processor<br>design and optimization. Application specific instruction set<br>processors- Microcontrollers- Digital signal processors                                                                                     | 7  | 15% |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

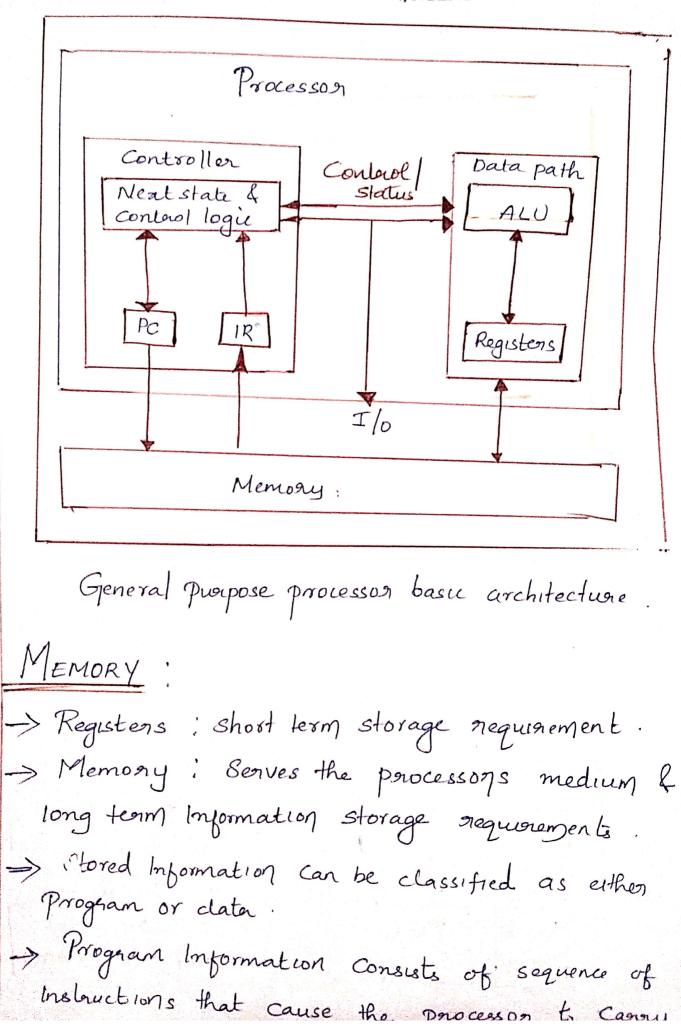

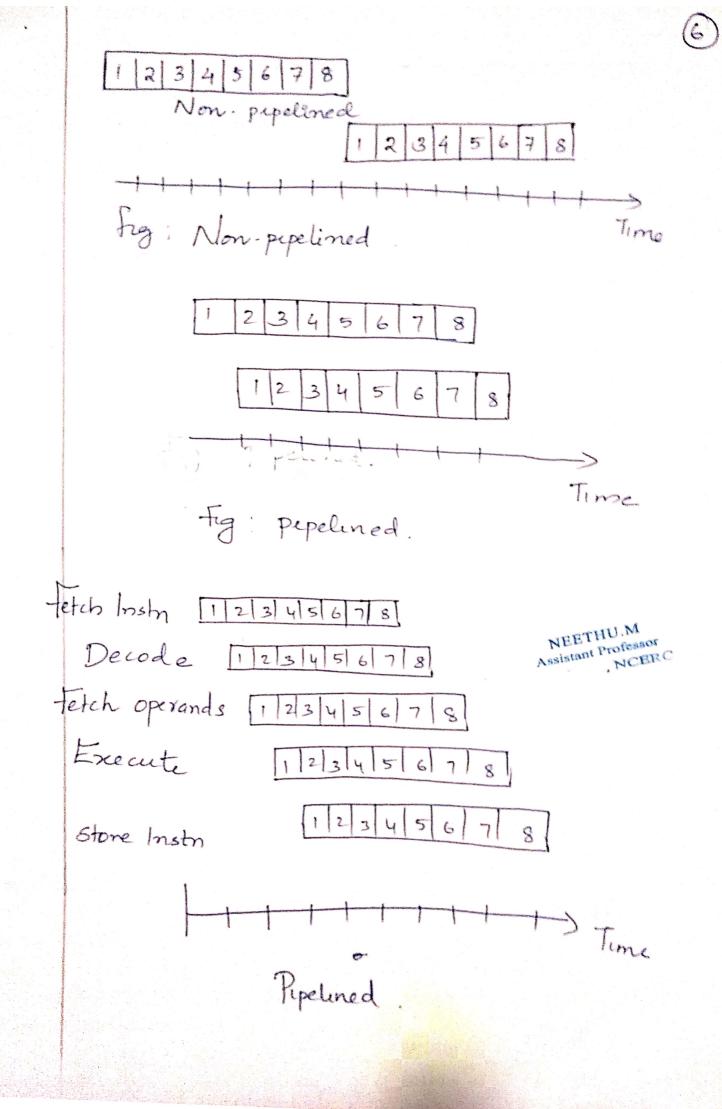

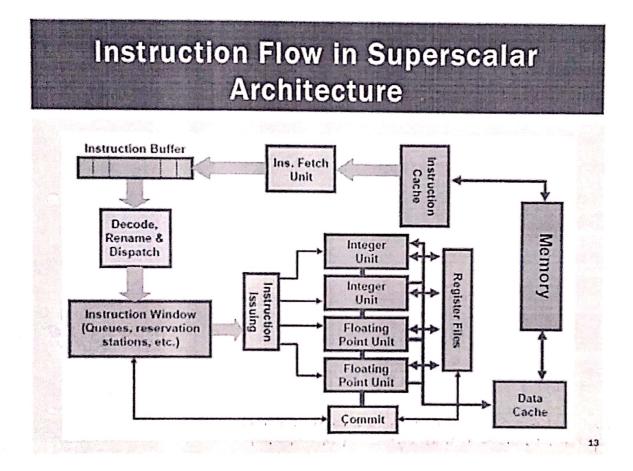

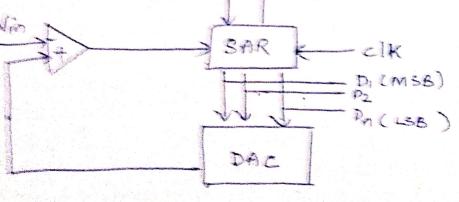

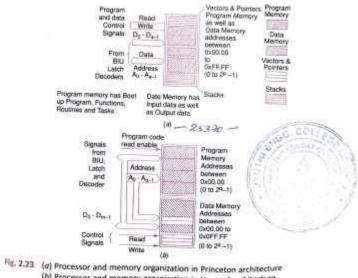

| IV | General-purpose processors: Software: Basic architecture-<br>Datapath- Control unit- Memory- Instruction execution-<br>Pipelining- Superscalar and VLIW architectures- Instruction<br>set- Program and data memory space- Registers- I/O-<br>Interrupts- Operating Systems- Standard single-purpose<br>processors: Peripherals-some examples such as Timers-<br>counters- Analog-digital converters. | 17 | 15% |

| v  | Common memory devices - Memory selection - Memory map -<br>Internal devices & I/O devices map - Direct memory access<br>Types of I/O devices - Serial devices - Parallel port devices -<br>Sophisticated features - Timer and Counting devices -<br>Advanced serial bus & I/O - High speed Buses - Common<br>types - Advanced Buses. | 7 | 20% |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

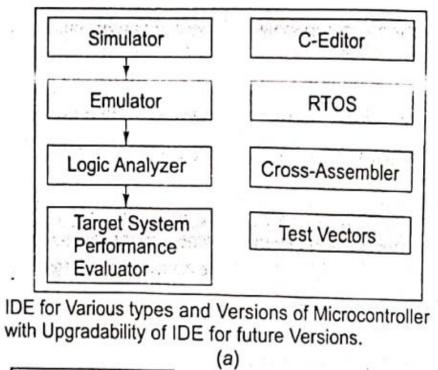

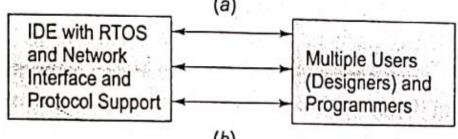

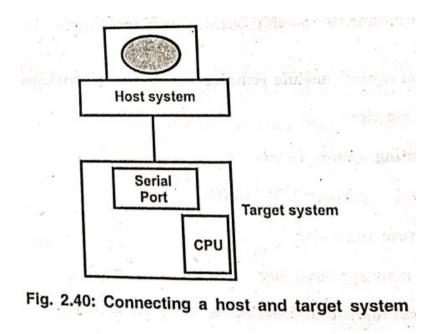

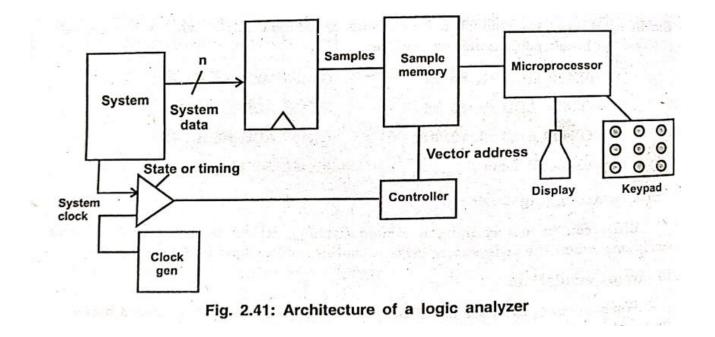

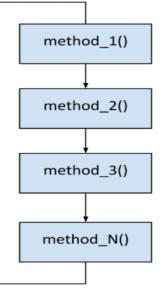

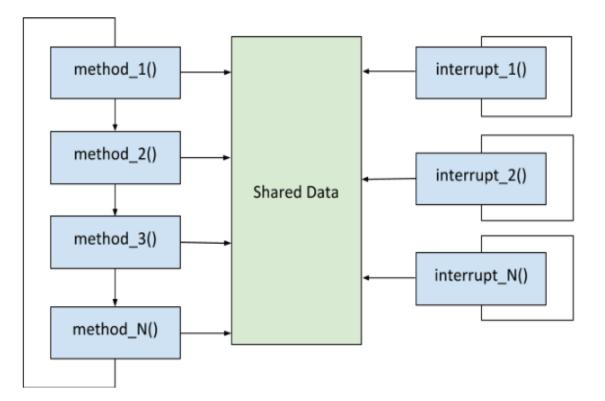

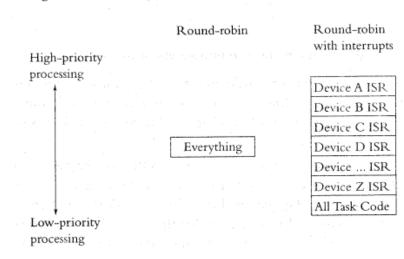

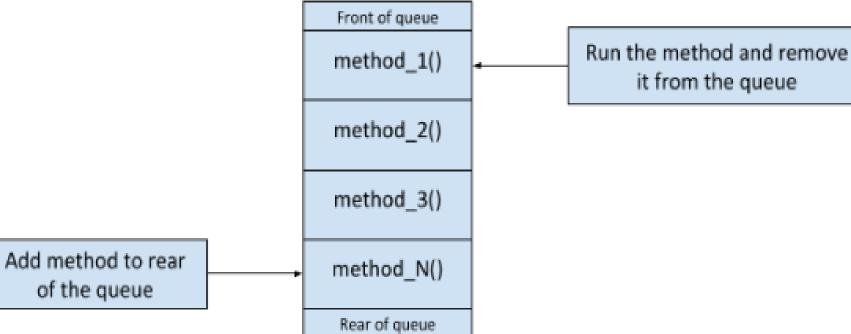

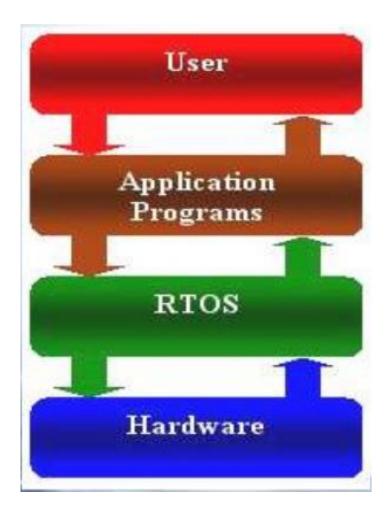

| VI | Development tools: Host and Target machines - linker /<br>locators - debugging techniques.<br>S/W Architectures: Round robin-round robin with interrupt -<br>function queue scheduling- RTOS.                                                                                                                                        | 7 | 20% |

# END SEMESTER EXAM

# QUESTION PAPER PATTERN

Maximum Marks: 100

Exam Duration: 3 hours

# PART A: FIVE MARK QUESTIONS

8 compulsory questions -1 question each from first four modules and 2 questions each from last two modules (8 x 5= 40 marks)

2014

# PART B: 10 MARK QUESTIONS

5 questions uniformly covering the first four modules. Each question can have maximum of three sub questions, if needed. Student has to answer any 3 questions

$(3 \times 10 = 30 \text{ marks})$

## PART C: 15 MARK QUESTIONS

4 questions uniformly covering the last two modules. Each question can have maximum of four sub questions, if needed. Student has to answer any two questions

(2 x 15 = 30 marks)

# **QUESTION BANK**

|           | MODULE I                                                                                    |     |    |          |  |  |  |

|-----------|---------------------------------------------------------------------------------------------|-----|----|----------|--|--|--|

| Q:NO:     | QUESTIONS                                                                                   | СО  | KL | PAGE NO: |  |  |  |

| 1         | Define embedded system                                                                      | CO1 | K1 | 14       |  |  |  |

| 2         | Explain challenges and applications of embedded system in detail                            | CO1 | K2 | 15       |  |  |  |

| 3         | Explain design process                                                                      | CO1 | K2 | 16       |  |  |  |

| 4         | Distinguish between requirements and specifications                                         | CO1 | K4 | 24       |  |  |  |

| 5         | Explain characteristics of embedded system in<br>detail and also mention its<br>application | CO1 | K2 | 15       |  |  |  |

| 6         | Explain system with an example                                                              | CO1 | K2 | 13       |  |  |  |

| 7         | Explain various levels of abstraction of embedded system                                    | CO1 | K2 | 16       |  |  |  |

| MODULE II |                                                                                             |     |    |          |  |  |  |

| 1         | Explain watching dog timer                                                                  | CO2 | K2 | 41       |  |  |  |

| 2         | Discuss about various forms of system memories<br>used in the embedded<br>processor         | CO2 | K2 | 42       |  |  |  |

| 3         | Discuss about components of embedded system hardware                                        | CO2 | K2 | 46       |  |  |  |

| 4         | Discuss embedded system on a chip                                                           | CO2 | K2 | 51       |  |  |  |

| 5         | Compare microprocessor and microcontroller                                                  | CO2 | K2 | 32       |  |  |  |

Department of Mechatronics Engineering, NCERC, Pampady

| 6         | Describe power source , clock oscillator and clocking units                                       | CO2 | K2 | 40 |  |  |

|-----------|---------------------------------------------------------------------------------------------------|-----|----|----|--|--|

| 7         | Discuss<br>a) Embedded processor<br>b) DSP processor                                              | CO2 | K2 | 35 |  |  |

| 8         | Discuss<br>a) media processor<br>b) ASSP<br>C) Multiprocessor using GPPS                          | CO2 | K2 | 38 |  |  |

|           | MODULE III                                                                                        |     |    |    |  |  |

| 1         | What is a processor? Explain the benefits of using custom single purpose processor                | CO3 | К2 | 56 |  |  |

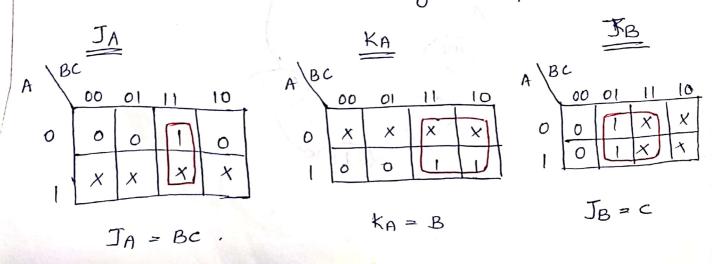

| 2         | Design a counter that counts 0,1,2,3,4,5,6 using JK<br>FF                                         | CO3 | K6 | 70 |  |  |

| 3         | Write a short note on steps involved in design of a combinational circuit using basic logic gates | CO3 | K2 | 57 |  |  |

| 4         | Explain CMOS implementation of some basic logic gates                                             | CO3 | K2 | 58 |  |  |

| 5         | Explain microprocessor                                                                            | CO3 | K2 | 32 |  |  |

| 6         | Explain digital signal processors                                                                 | CO3 | K2 | 35 |  |  |

| 7         | Explain multiplexer, decoder, adder, comparator, ALU                                              | CO3 | K2 | 64 |  |  |

| MODULE IV |                                                                                                   |     |    |    |  |  |

| 1         | Define operating systems                                                                          | CO4 | K2 | 98 |  |  |

| 2         | Compare Harvard and Princeton architecture                                                        | CO4 | K2 | 84 |  |  |

| 3         | Discuss about instruction execution                                                               | CO4 | K2 | 87 |  |  |

| 4 | Discuss about general purpose processor basic architecture                                | CO4 | K2 | 83  |

|---|-------------------------------------------------------------------------------------------|-----|----|-----|

| 5 | Discuss on a) registers b)input/output c)interrupts<br>d)program and data<br>memory space | CO4 | К2 | 97  |

| 6 | Discuss timers and counters                                                               | CO4 | K2 | 101 |

## **MODULE V**

| 1 | Explain Common memory devices              | CO5 | K2 | 114 |

|---|--------------------------------------------|-----|----|-----|

| 2 | Write a short note on Memory selection     | CO5 | K2 | 126 |

| 3 | Explain Memory map                         | CO5 | K2 | 138 |

| 4 | Explain Internal devices & I/O devices map | CO5 | K2 | 140 |

| 5 | Describe Direct memory access              | CO5 | K2 | 153 |

| 6 | Explain Types of I/O devices               | CO5 | K2 | 155 |

### **MODULE VI**

| 1 | Explain Real Time Operating System              | CO6 | K2 | 163 |

|---|-------------------------------------------------|-----|----|-----|

| 2 | Explain round robin with interrupt              | CO6 | K2 | 190 |

| 3 | Write a short note on host and target machine   | CO6 | K2 | 171 |

| 4 | Explain different debugging methods             | CO6 | K2 | 180 |

| 5 | Write a short note on linker and locator        | CO6 | K2 | 175 |

| 6 | Write a short note on function queue scheduling | CO6 | K2 | 199 |

### **APPENDIX 1**

### CONTENT BEYOND THE SYLLABUS

| S:NO | TOPIC                                      | PAGE NO: |

|------|--------------------------------------------|----------|

| 1.   | Programming concept in high level language | 216      |

Department of Mechatronics Engineering, NCERC, Pampady

# MODULE - I

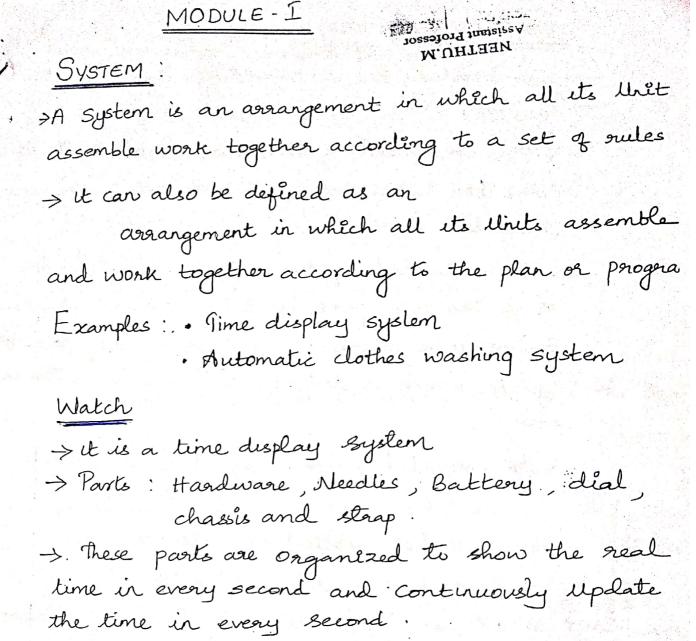

-> The system program updates the display Usin three needles after each second. it follows a set of rules.

Rules

N.0

1. All needles moves clockioise only 2. A thin needle rotates every second 3. A long needles rotates every minute 4. A short needle rotates every hour. 5. All needles networn to the orginal position after la hours

EMBEDDED SYSTEM > Embedded means something that is attack > An embedded system can be thought of as a Computer hardware system having software embedded in it > An embedded system can be an Independent syster or it can be a part of large system. An embedde. System is a mécro controller or microprocessor base System which is designed to perform a specific kash > An embedded System has three components · It has hardware , it has application Software · it has Real Time Operating System CRTO'S) that supervises the application software & provide mechanism to let the processor orun a process as per scheduling by following a Plan to Control the latencies -> BTOS defines the way the system works. it set the rules during the execution of application Program -> A small scale embedded system may not have RTOS -> So we can define an embedded system as a

NEET A ssistar

> Mécrocontroller based, Software doiven and reliable real time Control System.

Characteristics of Embedded System (2)(1) Single function. NEETHU.M Assistant Professor (2) fightly constrained (3) Reactive and real time (4) Microcontroller or microprocessor based (5) Memory (6) Connects Handware & Software Systems. (7)Single functions > it performs specialized Operations and does the sam Job repeatedly . lightly constrained -> The arcuit size should be small enough to fit on a single chip and must perform fast enough to process data en a real time and consume minimum power to extend battery life Reactive and Real time It should continuously react to the changes in the system environment and must compute certain results in realtime without any delay Macro controller on Macroprocessor based > Microprocesson are multi-tasking in nature, wherea Mecrocontroller are single task in nature > RAM, ROM, I/o ports, timens can be added externally and can vary in number in microprocessor

(2)Characteristics of Embedded System (1) Single function. NEETHU.M Assistant Professor (2) fightly constrained 1995 (1997 ) 135- AS Reactive and real time (3)(4) Microcontroller or microprocessor based Memory (5) (6) Connects Hardware & Software Systems. (7) Single functions -> It performs specialized Operations and does the sam Job repeatedly . lightly constrained -> The concuit size should be small enough to fit on a single chip and must perform fast enough to process data in a real time and consume minimum power to extend battery life. Reactive and Real time It should continuously react to the changes in the system environment and must compute certain results in realtime without any delay Macro controller on Macroprocesson based > Microprocesson are multi-tasking in nature, wherea Mecrocontroller are single task in nature. > RAM, ROM, I/o ports, timens can be added externally and can Vary in number in microprocessor

Scanned by CamScanner

>RAM, ROM, I/O ports, timens are added externally but these components are to be embedded together as a chip and is fixed in number in Micro contro Mer.

> In microprocessor, the designers can decide the number of memory and Ilo ports needed whereas there is fixed number of memory and Ilo ports which suits best for the Specific task in micro Controller.

> External Support of external memory or Ilo makes microprocessor based system heavier and Costger whereas they are light weighted and cheap in mecro controller.

Macroprocessor requires more space and consume more energy whereas microcontroller requires less space and less power.

Hardware & Software Systems : > Saftwares used in embedded System is generally for providing flexibility and extra features.

-> Hardware is used for performance and Security. <u>Memory</u>:

>It must have as memory as its Software Usually embeds in ROM . It does not need any Secondary memories in the Computer.

CHALLENGES IN EMBEDDED SYSTEM DESIGN > The challenges that are encounted during the design process are not computer related, rather they are mechanical on electrical. → of these, the most challenging areas are. (a) Hardware (b) deadlines. (c) power consumption (d) Upgradeability (e) Reliability. (a) <u>Hardware</u> (How much hardware do we need?) > The choice of the hardware plays a major role in meeting manufacturing cost constraints and Perfomance deadlines. -> The choice should n't be too expensive or too chea rather it should be exact to meet the deadlines. (b) Deadlines : ( How do we meet deadlines ) > Meeting deadlines is another challenge in designi an embedded computing system > one method of meeting deadlines is the brute force method". In this method the speed of the h/w is increased so that the program suns faster of course, that makes the system more expensive (C) Yover consumption : ( How do ve minimize Kover Consum > In battery-powered applications, power consumption is extremely important, even in non-battery applications, excess power consumption can increase heat dissipation. One way to make it consume less

Scanned by CamScanner

Power is to run slowly, but slowing down leads to missing deadlines. Therefore careful design must be done to meet performance goals. (d) <u>Design for Upgradability</u> (How do we design for Upgrad bility) > Designing a machine that can match with Upgrades in software is another challege > The same hardware may be used with different versions of the software

(e) <u>Reliability</u>: (Does & really works ) -> Reliability plays a vital role, if products are safety-critical products of these products lack reliability then the consequences can be Veny dangerous

> To ensure reliability, the designer must maintain an equilibrium between cost and the time.

Exp

# EMBEDDED SYSTEM DESIGN PROCESSES

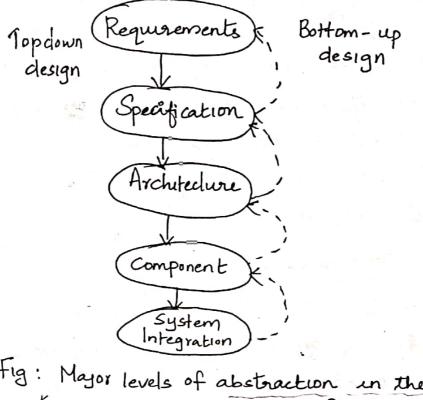

The major steps in the design process are summarized in the top down view as follows.

Fig: Major levels of abstraction in the design <u>Requirements</u> ' Process > The requirement phase of the design process Capture "what to design". > Informal description gathered from customers is known as "requirement". > Requirement can be of 2 types is, (a) Functional requirements (b) Non-Functional requirements > Some of the non - functional requirement are (1) <u>Power Consumption</u> : > In the requirement stage, power can be Specified where of battery life.

> However, the allounble voltages

wattage can't be

(4

Scanned by CamScanner

defined by the customer.

(2) Physical Size and weight:

> Depending on the application, the physical size and weight of the final system can vary a lot.

> if the application involves a handheld device then there are constraint on both the size and weight of the device. However, if it is an Industrial control system then there is no constr aint on the size and weight.

(3) performance

→ The cost and usability of the system are effected by it speed. The performance metaics can be combination of soft metaics and hard metaics (4) <u>cost</u>.

→ The System purchase price on the target Cost is very important. Complete Cost on Simply Cost includes The following two Components

a) Manufacturing cost

b) NRE (Non-Recurring Engnicearing) Cost.

Manufacturing cost is the cost of the Component NRE costs are the cost of hiring personnel and Other design related costs.

Requirements Validation :

-> Requirements Validation requires phychological Skills, as it deals with Understanding what custome

In the System requirement, the User interface pas Can be done by creating "Mock-up" > In order to stimulate functionality in a restricter area the mock-up make use of scanned data. -> This mock up can be executed either by PC o Work-station Requirement form / Requirement chart > The requirement form / chant acts like a checkle. when the project is in initial stages. A sample form is given below Name ; Purpose : \_\_\_\_ Cwhat the System Supposed to do Inpuls : \_\_\_\_ Outputs : \_\_\_\_ Functions : - C-functionality of the System). Performance : \_\_\_\_ Manufactusinglost : \_\_\_\_ Power: -Physical size & wt : \_\_\_\_ Fig : Sample Requirements form Name :- Name not only describe the purpose of the machine, but also helpful while commiting about the project Propose ! This should be a baref one on two line description of what the system is supposed to do

Scanned by CamScanner

Inputs and actputs: This field requires enformation about type of I/o devices, data characteristics and type of data Functions : A detailed des oription about the functionality of the machine is described on this field Performance : Inorder to assure proper functionality performance requirements should be identified before Rand and they must be measured Carefully Physical Size and weight ! Inorder to take archetedural decesions, the approximate physical size & weight of the system is important. Power : The rough idea about power consumption can be very helpful. Decision about whether the System is battery based or non-battery is important Rere SPECIFICATIONS -> spenfications serves as the contract between the customer and the archited > The specifications must be carefully worthen on that it accurately reflects the customers requirements > The specefication should be understanble enough so that Someone can Verify that it meets system requirement and overall of expectations of the Customer

> The specification of a GIPS system may include the following

- · Data received from the GIPS Satellite Sonstellatic

- · Map clata

- · User enterface

- · Operations that must be performed to satisfy customer requirements.

The differences between requirements and specifications

# Requirements Specifications. · An informal description · A Contract between Custome gathered from austomer and architecture. This is the forst step in design process · This is the second step in design process. · Requirements form is Used o UML is used to give clear to give a formal listing & proper specifications. of requirements · The description of project · The basic needs to design a system are given by is given by system System requirements specifications. . More Complex and · Less challenging task

· Requirements need not be perfect

· Good psycological skills are required to produce good system requirements challenging tast.

· Specifications should be

perfect enough in order

to develop correct application

· Good engeneering skills are

required to produce good

Specifications .

# ARCHITECTURE DESIGN

> The plan used to design the Components of a System is called as an architecture.

>It deals with how a system will perform the Specified Operations. Most of the designers have a perception that creation of the architecture is the first step of the design process.

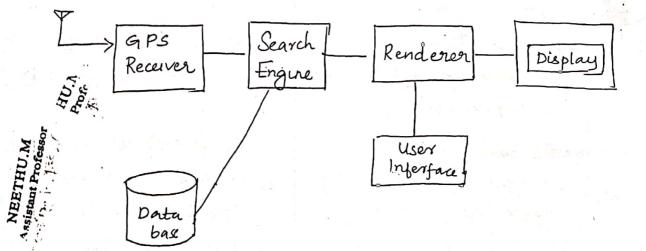

> The architecture is the plan for the Overall Structure of the System that will be used later to design the components that make up the architecture Example :

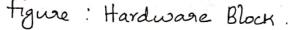

> Let us Consider the architecture of GPS maxing map in the form of block diagram which shows major operations are

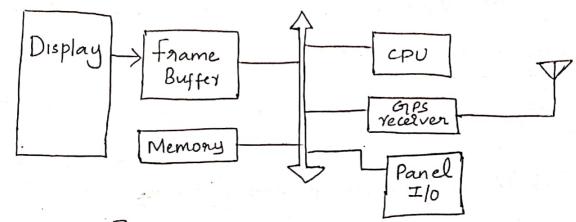

Blockdiagram of moving map > The before block diagram does not give clear picture about what operations are to be performed by the Software and Rardware. Inorder to have a clear picture, we have to Separate Rardware Operations from Software Operations.

Therefore 2 blocks are drawn here

Figure : Software block.

- > The refinement of hardware and software archite cture should begin only after the instial auchitecte is designed. > The hardware block diagram depict that memore and I/o devices sourronds the CPU. frame buffer holds the pixels to be displayed and memory for program data which will be used by the CPU. > Bus is Used to connect all these components > The software block diagram is same as initial architectus

- but an additional timer is added. This timer is meant for Controlling the Operations.

> finally both these block diagram should · Satisfy user requirements (functional Iron functional) , Include all the required functions-

Scanned by CamScanner

· should meet speed, cost, power requirements · Meet all the specifications DESIGNING H/W & S/W COMPONENT > The architectural description tells us about what components we need, -> The component design effort builds those component in conformance to the architecture & specification. > The components will be in general include both hardware - FPGIA's, boards and so on and Softwar module -> Some of the components will be ready made. > The CPU, for example will be standard component in all cases as well as memory. SYSTEM. INTEGRATION -> it deals with the integration or assembly of the components created. > Debugging is a challenge > However, good plaining, phase level development good test running at each phase can assist in finding bugs -> if bugs are identified and fixed at specified. time uterwals, then the task of debugging is not tig challenge and System Integration become casy

NEETHU.M sistant Profess

Ø APPLICATION OF EMBEDDED SYSTEM ? 1) House appliances : Washing machine (2) Automotive Industry : Antilock breaking system (ABS), engine Control 3) Home automation & Security systems : Air Condition , fire alagms. (4) Telecon : Cellular phones. 3 Computer pheriphagals : printers, Scamers. 6) Healthcare : EEG, ECG machines 7) Card readens : Barcade, Smart card readers 3) Embedded System for detecting rash dowing on highways . Here the speed checker device that edenlifies rash driving on highways and alarms the traffic authorities if the speed checker finds any Vehicle Violating the set speed limits on highways 9) Embedded system for street light control : To detect the movement of vehicles on high ways and to Switch on street lights ahead of it, and then to switch off the street lights as the Vehicle go past he street lights to conserve energy. ( PIC mecroconteroller is programmed by using embedded c)

NFETHU.M

DApplication of embedded System for Home: automation System. > Here home automation system with the andro application based remole Control > Remole operation is reaported by Indrived os based Smart-phone, upon a graphical user Interface based touch screen operation .. lopic :-functional building block of embedded s/m (Refer 11nd module : Embedded hardware Units) (Page: 6 to 8.) Both topics are same.

MODULE-II PROCESSORS -> A processor is a basic functional Unit in Computer system and Using that Unit only all the Computations take place -> A processor is the heart of the embedded System. So an embedded System designer must Rave clear knowledge of microprocessons and micro controllers -> A processor has 2 essertial Units () Program flow Control Unit (CU) (2) Execution Unit (EV) > The cu Includes a fetch Unit for fetching Instructions from the memory. The EU has Circuits that emplement the ensloudion pertaining to data transfer operations and data convension from one form to another form -> The EU encludes Arethmetic and logical Mart (ALU) and also the circuits that execute instructions from a program Control task. It can also execute Instructions for a call or branch to another program and for a Call to a function. >>> processor is mostly in the form of an IC chip on in core form in an ASIC. Core means a part of the functional Work on the VISI chip.

VARIOUS PROCESSOR : 7 Embedded System processon Application General purapose Applecation Specific Instruction Set Processor (GPP) Spenfre Processon (ASSP) Multiprocesson Processon System Using (ASSP) general purpose Core processors (GIPPS) V Microprocessor Minare 2 2 P Embedded Microcontr Digital Processon Oller Signal Embedded Media Processor Processon GENERAL PURPOSE PROCESSOR (GPP) > It is a programmable device used in a Variety of applications > Also known as "microprocessor" > features : 1) program memory @ General data paths with large register file and general ALU > User benefits : D Low time to market @ thigh flexibility.

(I) MICRO PROCESSOR

→ A microprocessor is a Single chip semi Conductor device also which is a 'Computer on chip, but not a complete Computer.

> its CPU contains an ALU, a program counter, a stack pointer. Some working register, a clock timing aircult and interrupt circulit on a single chip.

> To make complete micro computer one must add memony usually ROM and RAM, memony decoder an oscillator and no of sevial and parallel poots.

> It has the following instruction set:

① Instruction for data transfer operations

② Instruction for ALU Operations.

3 stack operations instruction set

(1) Input and Output (IIO) Operation Instanction set

(3) Program control Instruction set.

Sequencing and supervising Operations Instruction Set.

Figure purpose instruction set.

> A microprocessor is a single VISI chips that has a CPU and also have some other Unit that result in faster processing of instructions.

> Intel 8085 - 8 bit paocesson. It is used in older generation.

> Intel 8086 OR (-> 16 bit processor 8086 J

-> Intel 80x86 processors are the 32 bil of 8086. > The 'X' means extended 8086 for 32 bits Eg: 32 bit processons in 80 × 86 Serves are Intel 80386 and 80486. -> The IBM PCs are use 80x86 Series of processoris and embedded Systems in corporated Inside the PC for specifie tasks use these microprocessons. > An example of the new generation 32 and 64 bit microprocessor is the classic pertium series of processors from intel. These have superscalar architecture and also possess powerful ALU'S and floating point processing Unil Important Mecroprosser Used in the embedded Systems: Stream Microprocessor family Source

|          | Juving                             | Source         | both features.         |

|----------|------------------------------------|----------------|------------------------|

| Stream 1 | 68 HC <sub>XXX</sub>               | Motorola       | CISC                   |

| Stream 2 | a) 80x86<br>b) 1860                | Intel          | CISC<br>CISC WITH RISC |

| Stream 3 | SPARC                              | Sun            | RISC                   |

| Stream 4 | a) Power PC 601, 604<br>b) MPC 620 | IBM<br>Motorda | RISC                   |

-> An RISC processor provides speedy processing of the Instructions, each in a Single clock cycle.

$\rightarrow$

# (a) EMBEDDED PROCESSOR

> A special macaoprocessons & micro controllers often called, embedded processons. > An embedded processon is used when fast process fast context switching and atomic ALU Operations are needed.

Examples

• ARM 7 • INITEL 1960, AMD 29050 » For complex real time system normal microprocessors and micro controllers are not suitable. So Special Kind of processor known as Embedded processor are required.

>When a macrocontroller or microprocessor is Specially designed for complex system it has the following capabilities then the team embedded processor is preferred instead of microcontensiles \$99 microprocessor.

1) Fast context switching and thus lower latencies of the tasks in complex real time applications. 2) Atomic ALU operations & thus no shared data problem

3) Risc Core for fast, more precise & Intensive calculations by the embedded Software

> NEETHU.M Assistant Frofessor ECE Dept., NCERC

(3)

(1) DIGLITAL SIGNAL PROCESSOR (DSP)

- → DSP is an essential Unit of an embedded System in large number of applications needing processing of signal.

→ Eg: Applications are image processing, multimedia audio, video, HDIV, DSP modern and telecommunication. Processing Systems.

- → The DSP as a GPP is a single chip VLSI Unit. It possesses the computational capabilities of a mechophoces and also has a multiply and accumulate Units. → A DSP provides fast, discrete time, signal processing instructions. It has very large instruction word (VLIW processing capabilities. It processes the following thing in fast manner.

- 1) Single Instruction multiple data (SIMD) 2) Discrete Cosine transformations (DCT) 3) Inverse discrete Cosine transformations (IDCT)

Important DSP used in the embedded Systems.

Stream DSP family Source Stream 1 TMS320CXX, OMAP Texas stream 2 Tiger SHARC Analog device Stream 3 5600xx Motorola Stream 4 PNX 1300, 15002 Philips.

2 MICROCONTROLLER !

> A microcontroller is a functional computer system On a chip > it contains a processor memory and programmable Input/Output peripherals. > Microcontrollers include an integrated CPU, > A microcontroller is used when a small or part of the

embedded Software has to be located in internal memory and when the on-chip functional chits like Interrupt handler, port, timer, ADC are needed.

> Microcontrollers are particularly suited for use in embedded Systems for real time Control applications with on chip program memory and devices

Important Mecro controllers used in the Embedded Systems;

|          |                                          | 2 1 - A.          |                                     |

|----------|------------------------------------------|-------------------|-------------------------------------|

| Staeam   | Maconocontroller<br>-family              | Source            | CISC Or RISC<br>Or<br>both features |

| Stream 1 | 68 HCIIXXY HCIZXX<br>HCIGXX              | , Motorola        | CLSC                                |

| Stream 2 | 8051,80251                               | Intel             | CISC                                |

| Stream 3 | 80x86                                    | Intel             | CISC                                |

| Staeam 4 | PIC16F84 DY 16C76<br>16 F8 76 and PIC 18 | Microchip         | CISC                                |

| Stream 5 | Enhancements of<br>ARM9, ARM 7           | ARM,<br>Jexas etc | CISC with<br>RISC Core              |

NEETHU.M Assistant Professor ECE Dept., NCER

signal,

9

tion

Small scale Embedded System MET Microcontroller -1 V 8051 V V PIC 68HC05 16F8X 68HC08 Medium Scale Embedded System MicroController V 80196 68HCIIXX 8051 80×86 80251 G8HC12XX Large scale Embedded System NATION SOLUTION POWEY PC ARMJ MPC 604 Commonly used Microcontroller in small, medium & large scale embedded Systems. MICROPROCESSOR VS MICROCONTROLLER MICROPROCESSOR MICROCONTROLLER . A Includes functional blocks The functional blocks are of microprocessons and in ALU, registers, timing & addition it has timer, Control Units parallel 1/0, RAM, EPROM, ADC & DAC · Bit handling instruction is Many type of bit handling less, one or two type only Instauctions · Rapid movements of code & · Rapid movements of code & data between external memory data within microcontroller In Mecroparocesson . They are used for designing · it is used for designing application & pecific dedecated general Purpose digital Comparis s/m

MEDIA PROCESSOR

-> Media processor is a new innovative processor with high system performance for real time video performance, audio processing and data storeaning it also known as video processor.

> Media processor facilitatés a seamless fusion of mobile telephony with broad band internet . it facilitates voice based web accesses \_ Speech recognition, text to speech Conversation, VOIP (Voice Over Inkernet protocol) and voice based version of mobile ret standard XML.

- > A media processor should provide for the following processing functions:

- 1. VLIW, fixed as well as floating point agrithmetic

- 2. Discrete Cosine transformation (DCI) processing Unit

- 3. Quantiser Unit (Quantisation means analog signals from camera or microphone interface signals being converted to digital quantized output after encoding).

29) Processing of library functions for graphics, 20 text MPEG& MOTION JPG.

5) Image color and hue correction, image rotation, image scaling, shadow enhancement, detecting image edges & sharpening the image.

6) Video encoding which preprocesses for noise reduction and then controls the rate of transmission after estimating the motion picture rates, compresses\_ Synchronizes audio & finally bet streams are sort to a streaming network. 7) Video decoding, which neceives the bit stream £5 decompresses and separates audio and video £5 eliminates noise by preprocessing.

8) Noise neduction and echo cancellation.

APPLICATION SPECIFIC SYSTEM PROCESSOR (As.

→ Assp is dedicated to specific tasks and provide a faster solution.

→ An assp is used as an additional processing unit

running the application in place of Using embedded Software.

Examples: 11M7100, W3100A.

# MULIIPROCESSOR SYSTEM USING GPPS =

> Multiprocessors are used when a single processor does not meet the needs of difficult task.

-> The operations of all the processors are synchronized to obtain an optimum performance. EMBEDDED HARWARE UNITS

# EMBEDDED HARDWARE UNITS & TEMPORARY ASYSTEM

#### (1) Power Source

- Most embedded systems have a power supply of their own.

- The supply has specific operation range of voltages in one of the following 4 power ranges:

5.0 V ±0.25 V; 3.3 V ±0.3 V; 2.0 V ±0.2 V and 1.5 V ±0.2 V

- The propagation delay in the gates is inversely proportional to operational voltage;

therefore, the 5 V system is used in most high performance systems.

- Certain systems do not have a power source of their own, so they are connect to external power supply.

- For e.g. A Graphic accelerator do not have its own power supply.

### (2) Clock Oscillator Circuit (Clocking Units)

- The clock is an another basic unit of a system.

- A processor needs a clock oscillator circuit as the clock controls the time for executing an instruction.

- The clock controls the various clocking requirements of the CPU, system clocks and the CPU machine cycles.

- For processing units, a highly stable oscillator is required as the clock signal provides the synchronizing of all other system units.

(3) System Timers & Real-Time Clocks (RTC)

- To schedule the various system tasks and for real-time programming, a system clock or

Assistant Professor

- These clocks drives the timers for various timing & counting needs in a system. NEETHU.M ECE Dept., A

- System clock & RTC are also used to obtain delays and time-outs.

- A timer circuit is usually configured as the system-clock.

- Another timer circuit is suitably configured as the real-time clock (RTC) for periodic

saving of time & date in the system.

| - Microc               | ontrollers has built-in internal timer circuits                         | s for counting & timing devices.                              |               |

|------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|---------------|

| y, Reset &             | Inputdevices<br>Interfacing /<br>douver curcuits<br>Processor<br>Temens | Program memory<br>& clata »<br>Scaral cammuni<br>Catron ports | application . |

| ver suppl<br>oscellate | Interupt<br>Controller                                                  | Parallel posts                                                | Spe           |

| Power<br>0s            | Output Inkrfacue<br>desver circuite                                     | fig: The Compo                                                | nents of Es   |

# (4) Reset Circuit, Power-up Reset & Watchdog-Timer Reset

- Reset can be activated by an external reset circuit that activates on power-up (switching). on) the system.

- The reset circuit is a simple circuit (such as an RC circuit) whose output connects to the reset pin of the processor.

- To reset a processor, the reset circuit should activate for a fixed period of a few clock cyclc3 & then deactivate thereby making the processor's reset pin active and then deactivate.

- Reset can also be activated by any one of the following:

(i) Software instruction (e.g. RST instruction)

(ii) Reset after a time-out by a programmed timer known as a watchdog timer

- The watchdog timer is a timing device that resets the system after a predefined timeout of a few clock cycles.

- A watchdog timer reset is very essential in embedded systems because it helps in rescuing the system if the system program gets stuck due to a fault.

- On restart, the system can function normally.

- Most microcontrollers have on-chip watchdog timers

Reset means that the processor begins the processing of instructions from a starting address.

That address is one that is set by default in a processor on a power-up.

SCE Dept. From that memory address (start-up addresses), program-instructions are fetched following the reset of the processor. - In certain processors, there are two start-up addresses.

Assistant Prof

3

- One is for the power-up reset and the processor fetches the program bytes from this

- The other one is for after the execution of a "reset" instruction or after a time-out such as a watchdog timer based reset. - Here, processor fetches the bytes program bytes from this second address on executing the reset instruction or on the watchdog timer based reset.

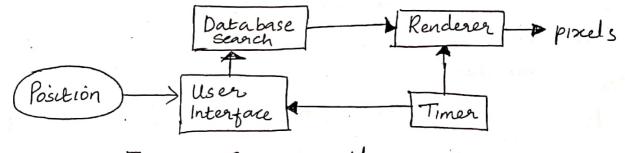

In a system, there are various types of memory and the figure shows a chart for various forms of memory hat are present in systems.

1. Internal RAM (of size in bytes) as internal registers in a microcontroller, temporary data storage (intermediate results/variables) & stack memory area.

2. Internal ROM/ PROM (of size in kB) for storing application programs in the case of microcontrollers.

3. External RAM for the temporary data storage and stack in the case of microprocessors.

4. Internal flash as 'non-volatile' memory to save the results after processing.

5. Memory stick (or memory card) as large storage (such as video, images, songs) in digital camera & mobile phones.

6. External ROM/ PROM for embedding software programs in almost all embedded systems except in microcontroller based embedded systems

7. Buffers memory RAM at ports.

8. Caches or cache memory (for storing copies of frequently used instructions & data)

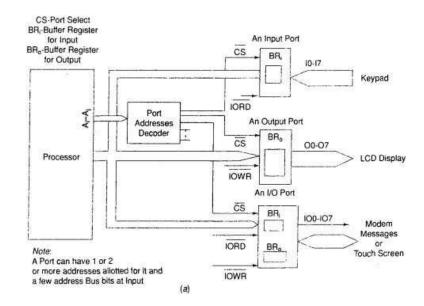

NEETHU.M Assistant Professor (6) Input, Output and 10 Ports, IO Buses and IO interfaces CE Dept., NCERC - The system gets inputs from physical devices through the input ports.

- Examples of inputs are

(1) A system gets inputs from the touch screen, keys in a keyboard, sensor

circuits etc

(2) A network card receives the input signals from a communication device such as a modem

(3) Ports receives inputs from a peripherals like USART.

- A processor identifies each input port by its memory addresses called port addresses.

- Just as a memory location, each input port is also identified by its address.

- The system gets the inputs by the read operations at the port addresses.

- The system has output ports through which it sends output bytes to the real world. (1) Output may be sent to an liquid crystal display (LCD) or touch screen display

panel or light emitting diode (LED)

(2) A system may send the output to a printer.

- (3) Output may be sent to a communication device such as a modem.

- (4) Some systems send the outputs to alarms, actuators etc.

- (5) A robot sent outputs for its various motors.

- Each output port is identified by its memory addresses (called port addresses)

- The system sends the output by a write operation to the port address.

- There are also general-purpose ports for both the input & output operations(IO ports)

- For eg., a touch screen sends output as well as gets input when a user touches displayed key on the screen.

- Each IO port is also identified by an address to which the read and write operations both take place.

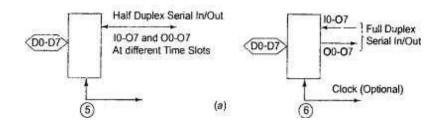

- Ports can also be serial or parallel communication

- In serial communication a one-bit data line is used and bits are sent serially in successive time slots.

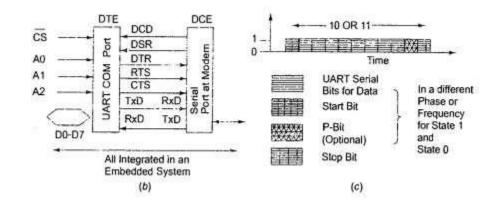

- Universal Asynchronous Receiver & Transmitter (UART) is a popular serial communication.

- In parallel communication, several data lines are used and bits are sent in parallel.

- A system connects to external devices and systems through parallel or serial I/O ports.

#### Bus

- A system has to be connected to a number of other external devices or systems.

A bus consists of a common set of lines to connect multiple devices, hardware units and other similar systems for communication.

A bus may be a serial or parallel bus that transfers data bit/bits.

- A "protocol" must be there to specify how signals communicate on the bus.

The protocol specifies (i) how bus is shared when several devices need to communicate through the bus (bus arbitration):

(ii) Ways of polling a bus from each device at an instance;

(iii) Ways of daisy chaining the devices so that bus is granted to a device according to the device-priority.

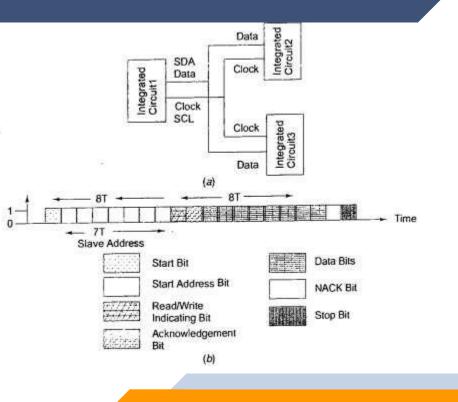

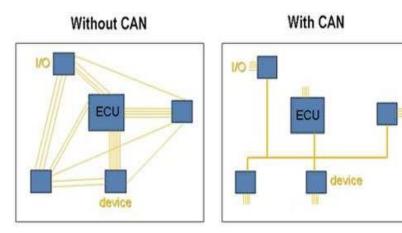

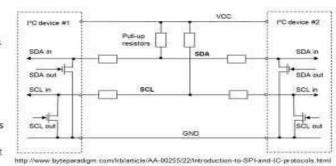

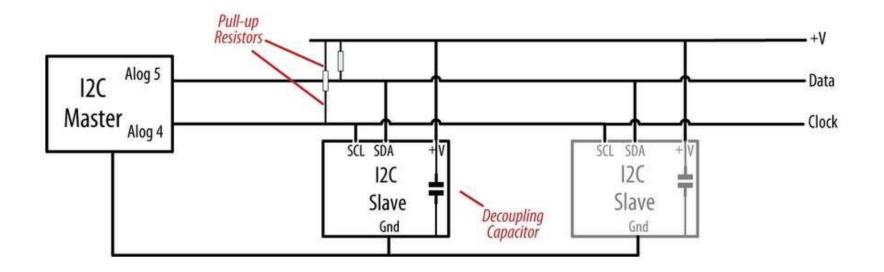

- A system networks to the other devices & systems through an I/O bus using different types of serial & parallel bus protocols such as 12C, CAN, USB, ISA, EISA & PCI bus.

# (7) DAC and ADC

- For controlling & signal processing applications, a system provides necessary interfacing circuits for the Digital to Analog Conversion (DAC) unit and Analog to Digital Conversion (ADC) unit.

- A DAC operation is done with the help of a combination of a PWM unit in the microcontroller and external integrator chip.

- ADC operations are required for data acquisition, image processing, voice processing, video processing, instrumentation and automatic control systems.

### (8) LCD, LED & Touchscreen Displays

- The system may need the necessary interfacing circuit and software to output to the LCD display, the LED interfacing ports or for the touchscreen I/O.

- A system has to display status messages in single line or in multiline.

- An LCD screen can show multiline display of characters, small icons etc.

- To indicate the ON status of the system, there may be an LED that glows.

- A flashing LED can indicate that a specific task is under completion or is running or in wait status.

- A touchscreen is an input as well as an output device, which can be used to enter a command, a chosen menu or to give a reply.

- The information is input by physically touching at a screen position using a finger.

- The "touch-screen" displays the choices or commands, menus and icons.

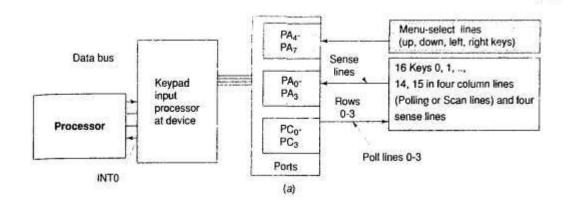

#### (9) Keypad/ Keyboard

- The keypad or keyboard is an important device for getting user inputs.

NEETHU.M Assistant Professor ECE Dept., NCERC

- For inputs, a keypad or keyboard may interface to a system.

- Necessary interfacing circuit & software must be provided to receive inputs directly from the keys or through a keypad controller IC.

- A keypad has upto a max. of 32 keys while a keyboard may have 104 keys or more.

- The keypad or keyboard may interface serially or parallely to the processor through ports and a keypad controller IC.

### (10) Pulse Dialer, Modem & Transceiver

- In communication systems, a pulse dialer, modem or transceiver is used.

- For user connectivity through telephone line network, system provides the necessary interfacing circuit and software for dialing of the modem and transceiver.

- A transceiver is a circuit that can transmit as well as receive byte streams.

#### (11) Interrupt Handler

- A system may possess a no. of devices connected as interrupts and the processor has to control and handle the requirements of each device by running an appropriate ISR (interrupt service routine).

- An interrupts-handling mechanism must exist in each system to the handle interrupts from various sources like external physical devices, software instructions etc. by executing the ISRs and for handling multiple interrupts simultaneously.

- Important points regarding the interrupts and their handling by the program are as follows.

1) There can be a no. of interrupt sources in a processor.

- An interrupt may be a hardware signal that indicates the occurrence of an event.

- An interrupt may also occur through timers, serial communication etc.

- The interrupt may arise due to an illegal op-code fetch, a division by zero result or an overflow during an ALU operation.

- A software interrupt may arise in an exceptional condition that may have developed while running a program.

2) The system may prioritize interrupt sources and service them accordingly.

3) Certain interrupt sources are not maskable and cannot be disabled.

Assistant Professor Assistant Professor ECE Dept., NCERC

- Some interrupt are assigned the highest priority during processing

4) The processor's current program has to divert to a interrupt service routine to complete that task on the occurrence of the interrupt.

5) There is a on-chip unit for the interrupt handling mechanism in a microcontroller.

6) The system always gives priority to the ISRs over the tasks of an application.

The operating system is expected to control the handling of interrupts and running of routines for the interrupts in a particular application.

# EMBEDDED SOFTWARE COMPONENTS

# **EMBEDDED SOFTWARE IN A SYSTEM**

- The software program code (instruction codes) is the brain of an embedded system

- An embedded system processor executes software that is specific to a given application

- The program codes are placed in the ROM (or flash memory or PROM) for the execution of tasks when the system runs

- This final "machine implementable software" is called the "ROM image" that is being embedded into the ROM similar to an "image" in an "image frame"

- Each program code is in bytes format & these bytes are saved at each address of the system memory (ROM)

- The code bytes are required at each ROM address to execute the tasks

- So, a machine implementable software file (ROM image) is similar to a table having many rows and only two columns; 1<sup>st</sup> column for memory address & 2<sup>nd</sup> column for corresponding code byte in a memory address

- By changing ROM image, the same hardware platform will work differently.

## Machine-code based coding

- In machine-code based coding, the programmer defines the machine code bytes corresponding each memory addresses for a program

- Machine-code based coding is done only in specific situations because it is time consuming and the programmer must have to understand the processor instructions set and their corresponding machine codes

# Coding in Assembly Language

- Small programs can be coded in assembly language after understanding the processor & its instruction set.

- These codes are also called low-level codes

the software used for converting the codes written in assembly language - "Assembler" is (similar to a compiler for high level language like C, Java etc)

- Assembly language coding is extremely useful for configuring devices like ports, ADC, NEETHU.M DAC etcant Professor

1

FBuf, Assembly language based programming is also very time consuming while making larger programs/ codes

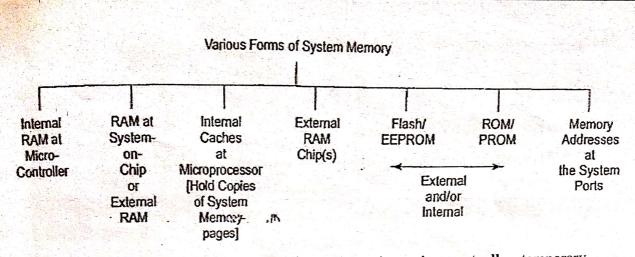

- Full coding in assembly may be done only for a few simple, small-scale embedded systems - Figure shows the process of converting an assembly language program into machine implementable software file and then finally obtaining a ROM image file

The process of converting an assembly language program into the machine codes and finally obtaining the ROM image

- Assembler, Linker, Locator & Loader are the software required for the whole process (1) 1st step is called "Assembling" in which an assembler software translates the assembly software into the machine codes

(2) Next step is called linking; a linker links these codes (if necessary) with the other codes taken from the library

- For a final program, a no. of other codes are to be linked together

- For eg., there are the standard codes for delay function (eg. delay() in Arduino)

- If 'delay()' is included in the program, the program codes for the delay() must

link with the final assembled code

- The linked file in binary is known as executable file (a file with '.EXE' extension) (3) In embedded systems, the next step after linking is the use of a "Locator" software which locates the already fixed ROM addresses

- For eg., in a memory-mapped IO scheme; IO port addresses, IO devices addresses etc. are permanently assigned to some memory locations

- The locator software "re-allocates" the memory addresses in a linked file & creates a file with permanent memory allocation for each of the code bytes in a standard format

Eg. for such a standard file format is "Intel .HEX file format"

(4) In the next step, the "Loader" software performs the task of placing/ loading the code bytes as an "image to be placed in ROM" by finding the exact available ROM memory

addresses

- For many processors, the available memory addresses may not start from "0000H"

- The "loader" finds the appropriate "start address" for the final program codes

- 2

(5) Lastly "Programmer Device/ Equipment" takes as input the ROM image file (For eg. in .HEX format) & "writes" the image as byte by byte into the memory - So the process of placing the codes into ROM or flash memory is also called "Burning"

10

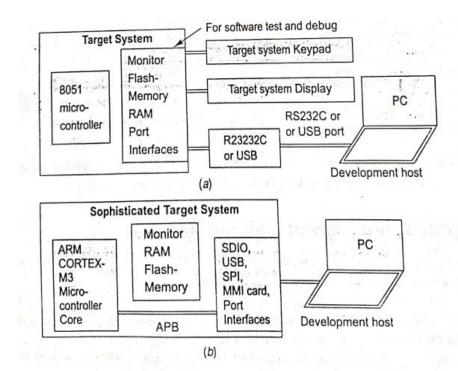

# Coding in High Level Language

- For large software programs development, high-level language like C, C++, visual C++, Java etc. are used

- 'C" is usually the preferred language

- The programmer needs to understand only the hardware organization of the wholw embedded system when coding in high level language

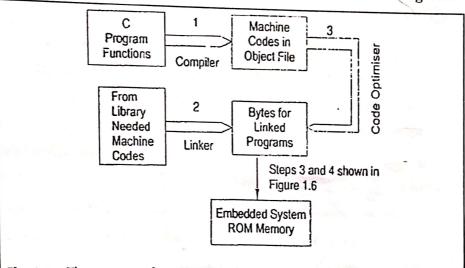

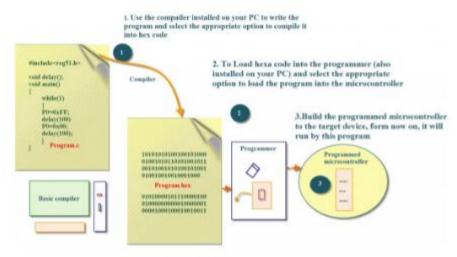

- Figure shows the process of converting a C program into the ROM image file

The process of converting a C program into the file for ROM image Fig. 1.8

- First, the compiler software generates the object codes (file with .OBJ extension)

- The compiler assembles the codes according to the processor instruction set

- Before linking, the compiler may use a "Code-Optimizer" that optimizes the codes by

removing the "redundant/ unnecessary variables or steps" written in the program

- The linker links the object codes with other standard program codes in the program (similar to the linking step in assembling process)

- For eg, the linker includes the program codes for the pre-defined functions like printf(), delay() etc

- Codes for some standard devices & the device control management also link at this stage;

- For eg., a printer device management & its driver codes

3

- After linking, the other steps for creating a file for ROM image are same as that discussed in previous section of assembling process (Locating, Loading & Burning)

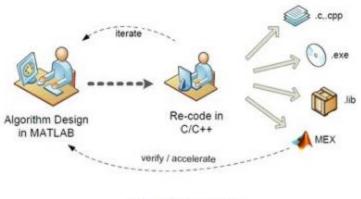

# GeriwARE GOOLS IN ES design:

> There are n number of tools used in designing an embedded system > it is Used in assembly language program 4 Righ level language programe 1) Editor Editor is Used for writing codes or assembly mnemonics using the keyboard of the PC for entering the program ->it allows the entry, addition, deletion, insert, appending previously waitten lines or files merging record and files at specific positions (2) Interpreter translation to the -> converts the line by line machine executable Codes. NEETHU.M Assistant Professor ECE Dept., NCERC 3 Compiler -> it converts the complete set of codes ento machine executable codes. it creates object file @ Assembler

(!)

It translating the assembling mnemonics into binary codes · It also creates a list file that can be printed · The list file has address, source code & Renadecimal object codes.

5 Cross Assembler 23 Mi 2001 -> it converts object codes or executable Code a processor to other codes for another processory Vice versa. 6 Simulator > To simulate all functions of an Es corcuit Include, additional memory and peripherals. -> it is independent of a particular target system. -> it also simulates the processes that will execute when the codes execute on the targeted particular pro cessor

⇒ tethoscope

⇒ used for dynamically tracking the changes in any program variable.

- it tracks the changes in any parameter. It demonstrate

the sequences of multiple processes that execute.

- it also records the enture time history.

§ Trace scope

→ used to help in tracking the changes in the madules & task with time on the X-axis → A list of actions also produces the desired time scales & the expected times for different tasks.

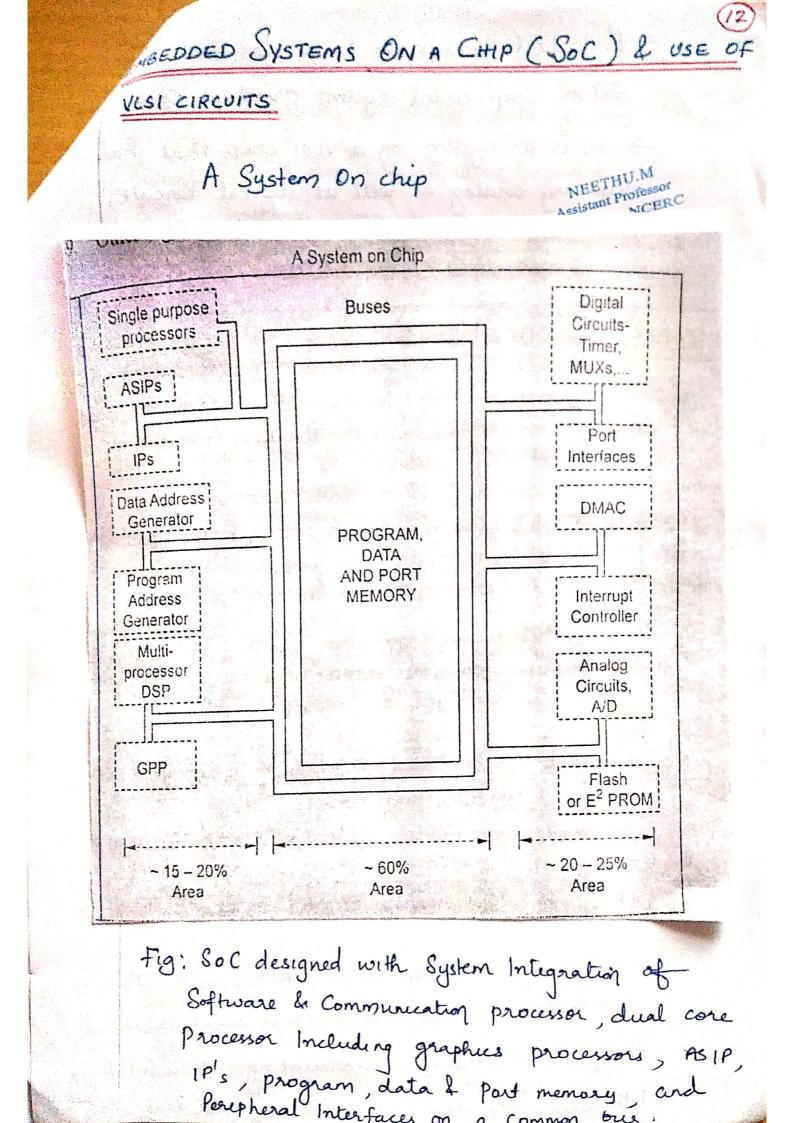

> Embedded System are being designed on a Single Silicon chip called System on chip (soc) -) Soc is a system on a VISI chip that has all the necessary analog as well as digital concurts, Processons and software. > A Soc may be embedded with the following Components. 1. Embedded processor GPP on ASIP Core 2. Single purpose processing cores or multiple processons. 3. A network bus protocol Core 4. An encryption function Und 5. Discrete Cosire transforms for signal processing applications 6. Memories 7. Multiple standard source solutions , called IP (Intellectual property) Cores. 8. Programmable logu device & FPGIA (field programmable gate Array) Cores. 9. Other logic & analog Units -> Application of such an embedded Soc is the mobile phone. -> Single purpose processors ASIPs and IPs on an Sol are configured to process encoding and deciphering, dialing, modulating, demodulating Interfacing the key pad and multiple line LCD

LCD matrix displays on touch soreen, storing data input and recalling data from memory. -> tig. shows an SoC that integrates Internal ASICS, Internal processons (ASIPS), Shared memories and perpheral Interfaces on a Common bus. > Besides a processor, memories and digital circuits with embedded software for specifie applications, the SoC may possess analog concurts as well. Application Specific IC (ASIC) -> ASIC's are designed using the VLSI design tools with the processor GIPP or ASIP and analog Corcuits embedded into the design → The designing is done Using electronic Design Automation (EDA) tool NEETHU.M Assistant Professor ECE Dept., NCERC IP core > On a VISI chip, there may be integration of high level Components. > These components possess gate level Sophistication in cocuits above that of the counter, regular multiplier, floating point operation unit and ALU > A standard source solution for synthesizing a higher level component by Configuring an

FPGIA core or a core of VISI concuit may be available as an Intellectual property called IP.

NEHRU COLLEGE OF ENGINEERING AND RESEARCH CENTRE (ACCREDITED BY NAAC)

PAMPADY, THIRUVILWAMALA, THRISSUR (DT), 680588

# **MR 405 EMBEDDED SYSTEM**

# MODULE III COURSE MATERIALS

SIGNATURE OF HOD

CUSTOM SINGLE PURPOSE PROCESSORS -> Processon Consist of 2 parits · Controller · Datapath. > Controller ; Controls the overall transfer of data through the data path. (le store & manipulate data) > Data path : can read data from a particular register and feed the data through functional Unit to Casay out a NEETHU.M Assistant Professor particular operation and stores back to the particular register. Réad data  $R_1$ > Functional Unit +/x- $\rightarrow R_{2}$ -> Single purpose prapessor is a digetal system Intended to solve a Specific Computation task. > Custon single purpose processor is to execute a specific lask within our embedded System. Eq: Digital camera Benefite of using custom single puopose processor: Derformance may be fast, due to fewer clock cycles resulting from a customized data path.

Scanned with CamScanner

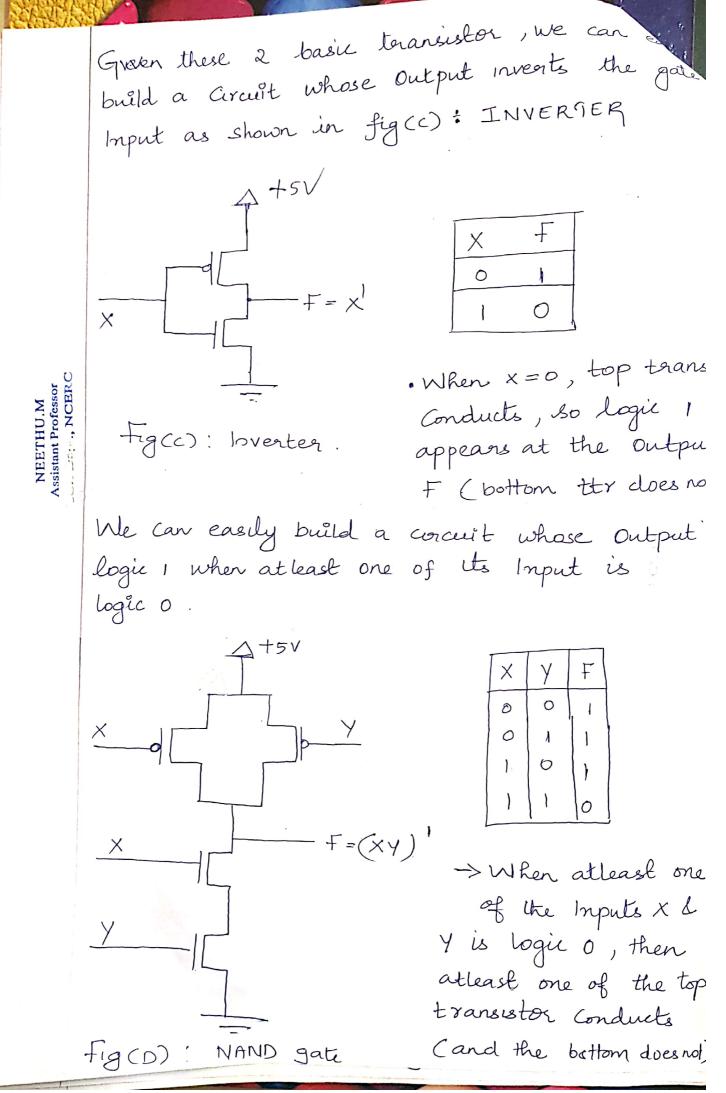

resulting simp @ Due to shorter clock cycles functional Units NEETHU.M 3 Less multiplexens Assistant Professor NCERC, NCERC (3) Simpler Control logie. (5) Stree may be small due to a simpler data path and no program memory 3 The processor may be faster and smaller than a standard one implementing the same functionality, since we can optimize the implementation for our particular kask BASIC TECHNIQUES FOR DESIGNING CUSTOM TROCESSORS tor this · start with a review of combinational and Sequential design · Describe a method for converting programs to Custom Single purpose processors. COMBINATIONAL LOGIC DESIGN . > A transistor is the basic electrical component of digital systems > Combinations of transistors form more abstract Component Called Logie gates, which designers primavily use when building digital systems.

Scanned with CamScanner

> A thansistor acts as a simple ON/off switch. > CMOS (Complementary Metal oxide Servi Conductor), combination of p-Mos & N-MOS. CMOS Implementation of some basic logic gates :gate \_\_\_\_\_ Conducts y gate = +5v -> Gate controls whether or not current flows from Source to drain -> When a high voltage drain tig(a): n-mos transistor (typically +5V), which is referred to as logic 1 is applied to the gate, the tonansiston conducts So Current flows. > When a low voltage (logic 0) is applied to gate, transistor does not conduct. We can also build a transistor with the oposite Functionality Surce gate Conducts -> When logic 0 is applied to gate, the transcelor ] gate = 0 y. Conducts -> When logic 1 is applied drain to the gate, the Fig(b): P-mos bransistor tranistor does not Conduct.

Scanned with CamScanner

Scanned with CamScanner

So logic 1 appears at f. > if both inputs are logic 1, then neither of the top transistors conducts, but both of The bottom ones do, so logie o appears ati F. We can easily build a circuit whose output is logie 1, when both of its mputs are logic 0.  $\propto$ 1 0 0 0 0 D 0  $f = (x + y)^{T}$ tig (E) : NOR gate > The 3 concerts shown implement 3 based logie galés ; an inverter, a NAND gate and a NOR gate

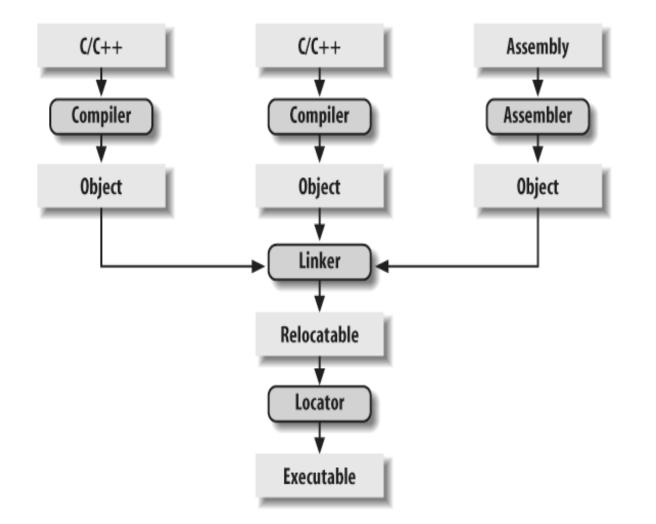

Figure 4.2: Basic logic gates <u>у</u> 0 Х 0 0 x 0 0 0 0 0 0 0 0 1 1 1 0 1 1 0 0 0 1  $F = x \oplus y$ 1 0 1  $\mathbf{F} = \mathbf{x} + \mathbf{y}$ - 1 0 0 1 F = x y0 XOR OR AND Driver F x 0 <u>у</u> 0 F <u>y</u>) x 0 у 0 F 1 х 0 1 1 0 1 0 F = x + y0 0 1 0 0 1 0 1 1 0 1 0 XNOR 1 0 F = (x+y)'NOR 0 0 F = x1  $\mathbf{F} = (\mathbf{x} \mathbf{y})^{T}$ 0 1 1 0 Inverter NAND NEETHU.M Assistant Professor > Digital system designers usually work with logie gates, not transistors. Each gate is represented Symbolically, with a boolean equation truth table and with a > A combinational concret is a digital concret whose output is purely a function of its avoient inputs : such à concuit has no memory of Past inputs Simple technique to design a combinational concret Using basic logic gates Step 1: problem description, which describes the Outputs interms of ioputs Steps: (irranslate the descruption to a truth table with all possible combinations of input Values on the left and descored output Scanned with CamScanner

410) terms of the enputs Output values on the rugh for each oulput Column, we can desure Step 3 an output equation with one term per grow. Minimize the Output equations by step 4 algebrucally manipulating the equis ., NCERC Assistant Professor NEETHU.M (Use Karnaugh maps) Draw the Concurt diagram. 5 Step / Deale Figure 4.3: Combinational logic design. (d) Minimized output equations (a) Problem description у 11 10 bc 00 01 y is 1 if a is equal to 1, or b and c is а equal to 1. z is 1 if b or c is equal 0 0 0 0 1 to 1, but not both. If a = b = C = 1=Z= 1 1 1 1 (b) Truth table y = a + bc00 11 Z 10 Outputs bc 00 01 Inputs а z b 0 1 0 0 1 0 0 0 0 0 0 0 1 0 1 1 1 1 0 0 1 0 0 1 0 0 1 1 1 z = ab + b'c + bc0 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 a b (c) Output equations y = a'bc + ab'c' + ab'c + abc' +Z abc z = a'b'c + a'bc' + ab'c + abc' +abc

-> Although we can design all combination assaults in the above manner large concults would be Very Complex to design > A concuit with 16 inputs would have 2<sup>16</sup> or 64K gows in the truth table > one way to reduce the complexity is to use Components that are more abstract than logic gates -> Several Such Components ane NEETHU.M Assistant Professor NCERC D Multiplexer / Selector -> Allows only one of its data enput Im to pass through to the Output O > Multiplexed acts much like a rail road Switch, allowing only one of multiple isput tracks to Connect to a single Output track Eq: 8:1 MUX MUX 4:1 -> if there are m data inputs, then there are log(m) Select lines S and we call this an mby 1 multiplexer (m data inputs and one data Output). -> The binary value of s determines which data

Input passes through: 00;00 means IO may pass 01;01 11 II 11 11

(2) Decoder

-> Decoder converts its binary input I into a One-hot Output O > "one-hot" means that exactly one of the Output lines can be 1 at a given time. -> Thus, if there are n. outputs, then there must be log(n) inputs NEETHU.M > Eg: 3x8 de coder Assistant Professor , NCERC 3 inputs & 8 Outputs Adder ! > An adder adds two n-bit binary inputs ABB generating an n-bit Output sum along with an Output casary Eq: 4 bit adder A=1010 & B= 1001, then SUM S= 0011 and carry = (4) Comparator -> A comparator compares two n-bit bibary inputs A & B generating Outputs that Indicate whether A is less than, equal to or greater than B. 5 ALU (Arthmetic logic Unit) -> can perform a Variety of arithmetic

(7

Scanned with CamScanner

logic functions on its n-bit Input A and > Common functions includes addition, Subtraction, etc Figure 4.4: Combinational components. I(log n -1) 10 I(m-1) I1 I0 B В n · n · n n n S0 n-bit, m x 1 n bit, m function 🛃 log n x n n-bit n-bit ALU Multiplexor Decoder Adder Comparator S(log m) S(log m) n O(n-1) O1 O0 0 carry sum less equal greater 0 0 = O0 =1 if I=0..00 sum = A+Bless = 1 if A < BO = A op BI0 if S=0..00 O1 =1 if I=0..01 (first n bits) equal =1 if A=Bop determined I1 if S=0..01 carry = (n+1)'thgreater=1 if A>B by S. On =1 if I=1..11 bit of A+B Im if S=1..11 CERC enable input e carry-in inputCi status outputs all O's 0 if e=0 sum=A+B+Ci carry, zero, etc. n-1 means ... n wires EQUENTIAL LOGIC DESIGN -> A sequential circuit is a digital circuit whose Outputs are function of the cuovant as well as previous inputs values It possesses memory > The sequential components are shown in figure below fig (4.5)

Figure 4.5: Sequential components. n NEETHU.M n-bit n-bit n-bit Register Shift register Counter 0 clea Q Q =Q = 0 if clear=1, 0 if clear=1, I if load=1 and Q(prev)+1<sup>·</sup> clock 8, if count=1 I(prev) else. and clock 8. > One of the basic sequential cigavits is the flup flop -> A flipflop stores a single but The Sequential Components are (1) Register > A register stores n-bits from its n-bit data I, with those stored bits appearing at its Output > A register usually has at least two control inputs, clock and load > For a rising edge treggered register, the Input I are only stored when load is I and clock is rusing from 0 to -> clean : resets all bits to 0, regardless of the Value of I > Because all nuts of the register can be stored Parallel, we often refer to this type of register N Parallel baad register as α

(3) Shift register

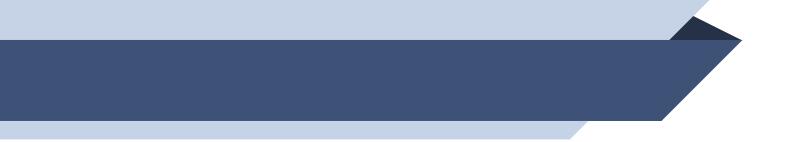

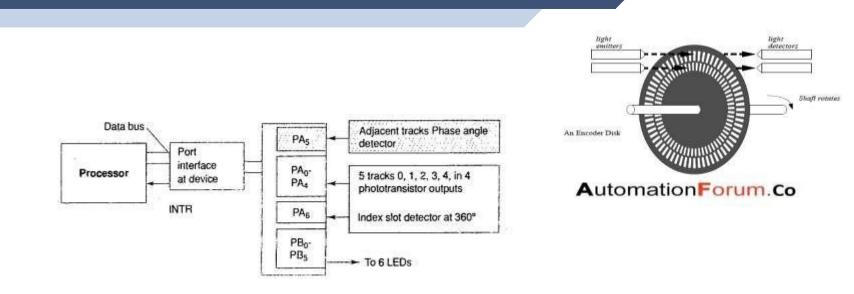

> stones n bits, but these bits cannot be stored in parallel. Instead they must be shifted ento the register serially, meaning one bit per clock edge > A shift negister has a One-bit data input I and atleast two control inputs clock and shift. > When clock is susing and shift is I, the value of I is stored in the nth bit, while the nth but is Stored in the (n-1) the but and likewise, until the Second bit is stored in the first bit. > The first bit is typically shifted out, meaning it appears over an Output Q (4) Counter NEETHU.M Assistant Professor > A counter is a register that can also increment (add binary 1) to its stored binary value > A counter has a clear input, which resets all Stored bits to 0, and a count input, which enables Incrementing on the clock edge > A Counter often also has a pagallel load data Input and associated control signal > A common counter feature is both up and down Counting (Incrementing & decrementing) required an